电子元器件公司 2024-09-06 23:59:02

74LS74是一种数字逻辑集成电路,具有两个D触发器功能单元。每个触发器单元有一个数据输入(D)、一个使能输入(EN)和两个输出(Q和另一个Q')。该芯片的管脚功能如下:

1. 1D和2D:这两个是两个触发器单元的数据输入端。将要存储的数据输入到这两个管脚上。

2. 1EN和2EN:这是两个触发器单元的使能输入端。当使能端为低电平时,触发器单元才能工作;当使能端为高电平时,触发器单元将保持其当前状态。

3. 1CLK和2CLK:这两个管脚是两个触发器单元的时钟输入端。当时钟输入端发生上升或下降沿时,触发器单元才能读取数据并更新其状态。

4. 1Q和2Q:这两个是两个触发器单元的输出端。它们分别输出相应触发器单元的当前状态。

5. 1Q'和2Q':这是两个触发器单元的补反输出端。它们输出与相应触发器单元的当前状态相反的值。

搭配74LS74的常用电路有:

1. 序列寄存器:将多个74LS74级联,连接时钟信号形成一个寄存器,可以实现数据的串行传输和存储。

2. 数据锁存器:将74LS74配置为边沿触发的D触发器,使得当时钟信号上升沿或下降沿到达时,输入数据被锁存和存储。

3. 分频器:通过适当设置使能输入、时钟输入和数据输入,可以实现74LS74的分频功能。

4. 时序发生器:结合其他逻辑门电路,利用74LS74实现特定的时序逻辑功能,例如计数器、状态机等。

当搭配使用74LS74时,需要根据具体的应用需求,合理设置触发器单元的使能、时钟和数据输入。同时,还需要注意时钟信号的稳定性和触发器之间的电路连接,以确保正确的数据传输和触发器状态更新。

电子元器件质量检测机构,电子元器件模块检测中心?

2025-04-06

电子元器件CE认证?

2023-10-08

2024年德国慕尼黑国际电子元器件展ELECTRONICA?

2023-09-06

成都供应电子元器件防震防静电运输袋导电膜复合气泡袋?

2023-06-30

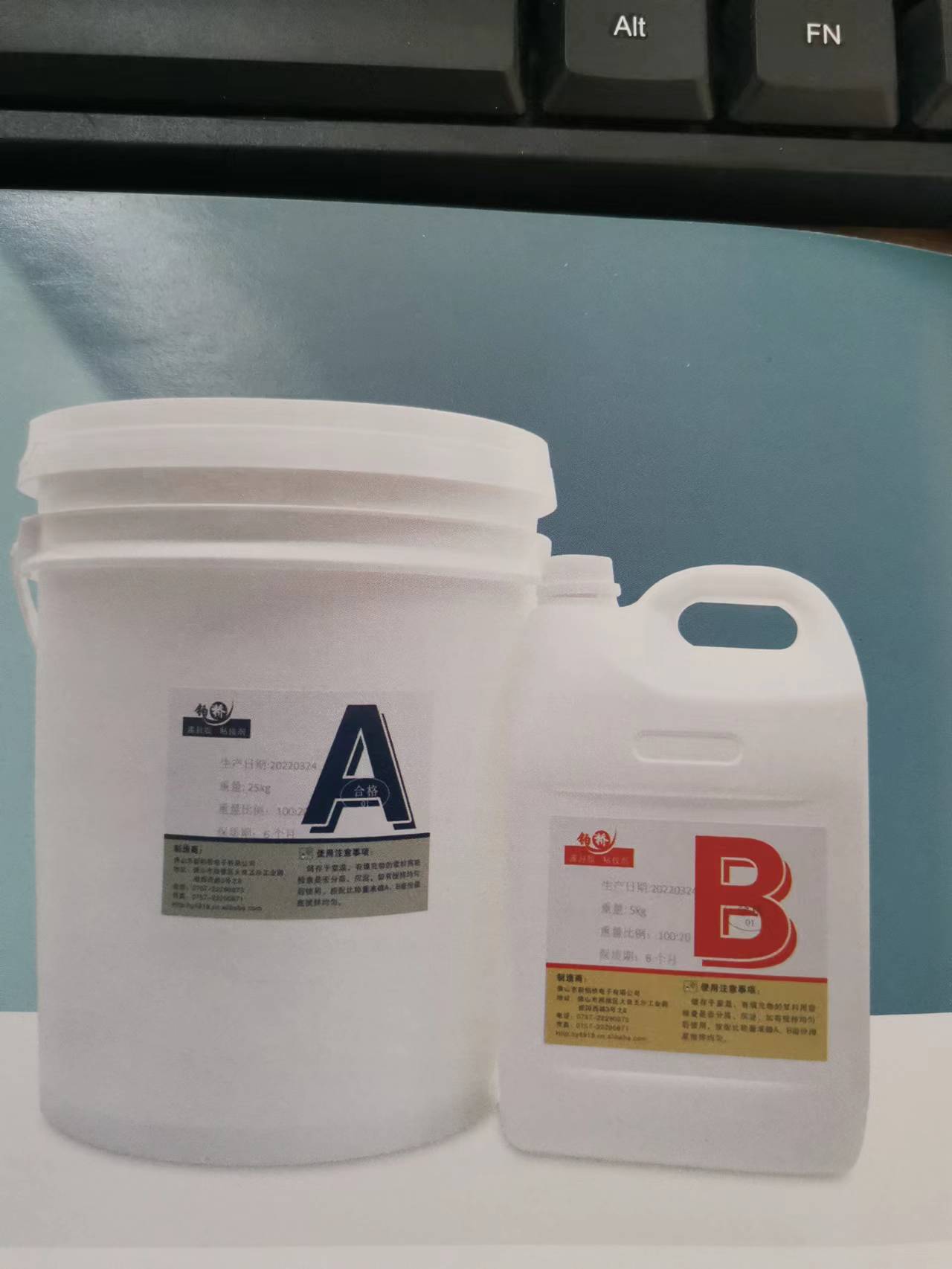

深圳电子元器件灌封胶,耐高温胶水,互感器灌封胶厂家?

2023-03-03

电子元器件防静电吸塑托盘 电脑主板用防静电托盘上海永怡?

2022-12-28